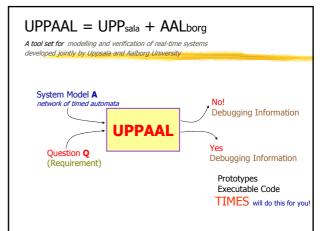

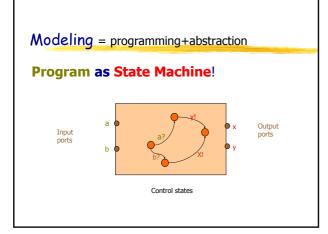

## Modeling and Verification of Real Time and Embedded Systems

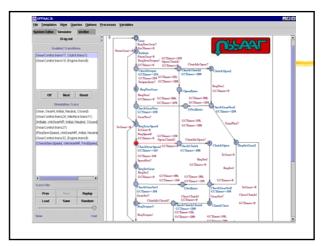

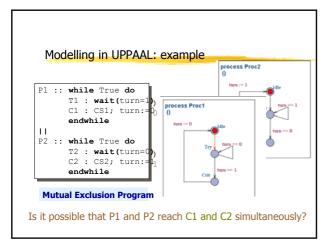

A tutorial on UPPAAL

Wang Yi Uppsala University, Sweden, 2005

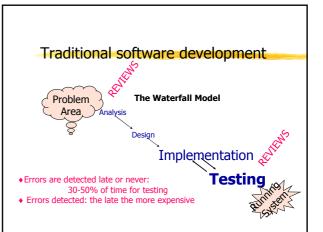

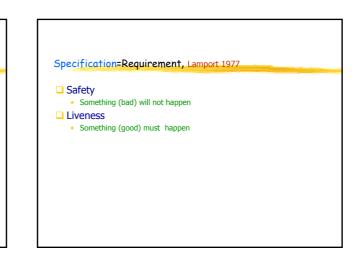

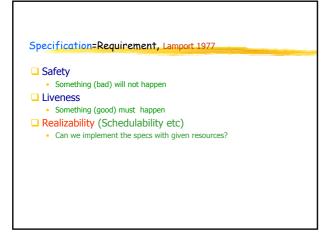

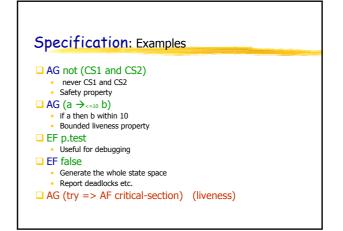

**SPECIFICATION**

How to ask questions: Specs ?

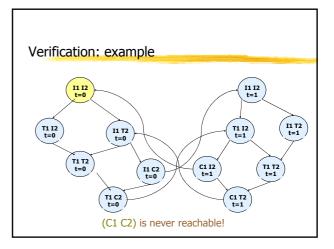

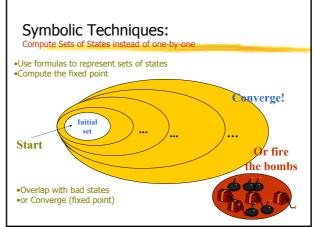

## Verification

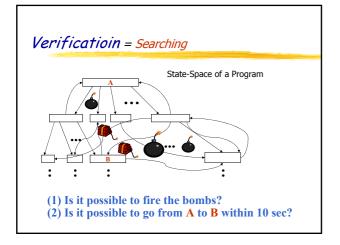

- Semantics of a system

- = all states + state transitions (all possible executions)

## Verification

= state space exploration + examination

# OUTLINE

### Introduction

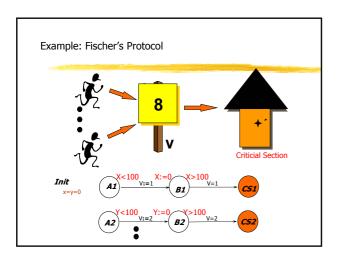

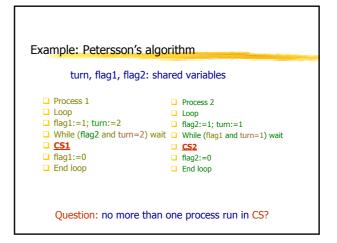

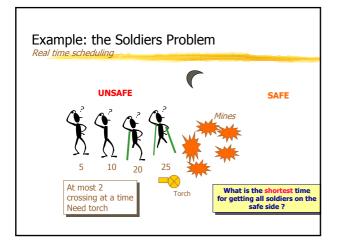

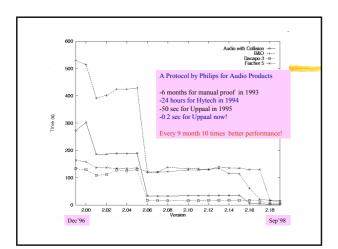

Lecture 1: Motivation, examples, problems to solve

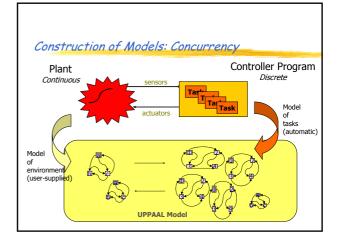

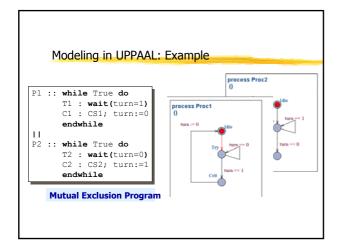

### Modeling and Verication of Timed Systems

- Lecture 2: Timed automata, and timed automata in UPPAAL

- Lecture 3: Symbolic verification: the core of UPPAAL

- Lecture 4: Verification Options in UPPAAL and/Or Demo

#### Towards a Unified Framework

Lecture 5: Modeling, verification, real time scheduling, code synthesis

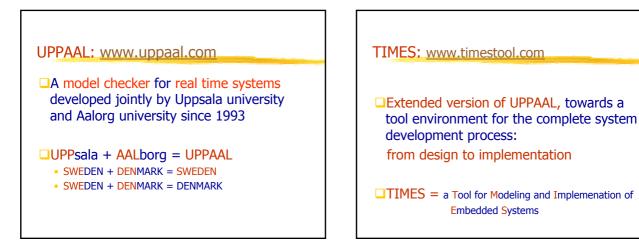

From UPPAAL to TIMES